오늘은 연산증폭기라고 하는 새로운 소자에 대해 알아볼 것이다.

전공자들은 주로 OP-Amp ('오피 앰프'라고 읽으면 됨)라고 부르는 이 놈 !

회로관련 과목 뿐만 아니라 통신, 제어 등 다양한 분야에서 사용되므로 기초를 튼튼히 해놓으면 좋다.

각설하고 자세히 살펴보자.

연산 증폭기(OP-Amp)란?

OP-Amp란 Operational Amplifier의 약자로 직역하면 연산 증폭기라는 의미이다.

연산을 증폭 시킨다고?

어떤 연산을 어떻게 증폭시킨다는거야??

정답은 빼기(-)를 증폭시킨다.

이를 이해하기 위해선 OP-Amp의 핀과 구조에 대해 알아야한다.

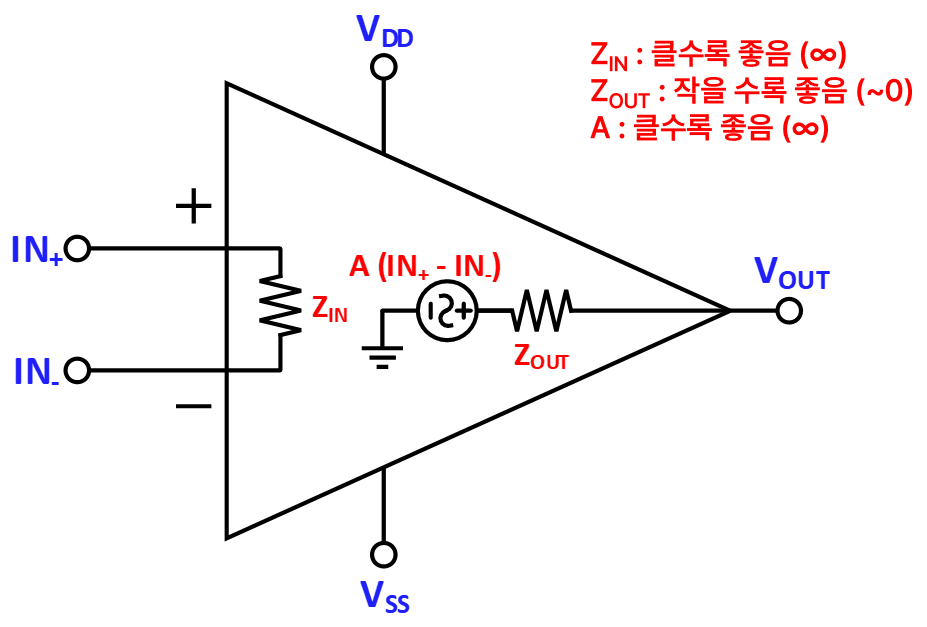

통상적으로 OP-Amp는 5개의 핀을 지닌다.

IN+ : 입력 신호를 받는 핀이다. (+)라는 기호는 구분을 위한 것일 뿐 양수를 뜻하진 않는다. 정식 명칭은 비반전(Noninverting) 입력단자 이다.

IN- : 마찬가지로 입력 신호를 받는 핀이다. (+)핀과의 구분을 위해 (-)라는 기호를 사용하며 음수를 뜻하는 것이 아니다. 정식 명친은 반전(Inverting) 입력 단자이다.

VOUT : 출력 신호를 나타낸다. 연산의 결과로 증폭된 신호가 할당되는 핀이다.

VDD : 전원핀이다. 연산 증폭기의 동작에 필요한 전력을 공급하는 핀이며 동작 범위에도 제한하는 역할을 한다. VCC로 표현하는 경우도 있다.

VSS : 이 핀도 전원핀이라고 생각하면 된다. 사용하는 전압의 크기에 따라 음수가 될 수도 있고, 0V(GND, 그라운드, 접지핀)으로 연결되기도 한다. VDD와 마찬가지로 OP-Amp의 동작 범위를 제한한다. VEE로 표현하는 경우도 있다.

기호로 표시할 땐 가끔씩 전원핀 VDD와 VSS는 생략하기도하는데, 그 경우 해당 회로의 전원으로 선언된 핀이 해당 핀에 공급된다고 생각하면 된다.

??? : 어라? 가운데 적힌 A는 뭔가요?

이제부터 설명하겠다.

전압 이득(Voltage Gain)

앞서 연산증폭기는 '빼기' 연산을 증폭시킨다고 했다.

입력 신호를 받는 두 단자 IN+의 전압과 IN-의 전압의 차이를 A배 증폭시킨 후 이를 VOUT으로 내뱉는 소자이다.

이때 작은 전압을 증폭시켜 큰 전압을 얻으므로 A를 전압 이득(Voltage Gain)이라고 한다. (단위는 V/V이다.)

별다른 표시가 없다면 이상적인 회로에서 A는 무한대(∞)의 값을 갖는다.

하지만 실제론 아니다.

그것이 가능하다면 원자력 발전소는 필요가 없지...

간단하게만 생각해도 전원으로 공급하는 것 이상의 전압을 생성해낼 수는 없다.

(VDD와 VSS 내에서만 증폭이 가능하므로 무한대의 전압 이득은 사실상 불가능하다.)

하지만 매우 큰 이득을 갖고있다는 것을 이용해 유용한 회로들을 만들 수 있다.

우선은 OP-Amp의 특징에 대해 쫌 더 살펴보자.

연산 증폭기(OP-Amp)의 특징

일단은 딱 두가지만 기억하라.

① 보통 두 입력 단자 사이의 전위차가 없다. (= 전압이 같다.)

② 두 입력 단자로 전류가 들어가지 않는다.

다른 핀인데 전압이 같고 신호를 넣었는데 전류가 들어가지 않는다고?

직관적으로 잘 이해가 가지 않을 수 있다.

한 구절씩 살펴보자.

① 보통 두 입력 단자 사이의 전위차가 없다. (= 전압이 같다.)

정확하게 말하면 '거의' 전위차가 없다는 표현이 맞겠다.

OP-Amp는 두 입력 단자 사이의 신호차를 무한대에 가깝게 증폭시킨다고 했다.

두 단자 사이의 아~~~주 작은 신호를 증폭시키는 행위이므로 거시적으로 봤을 때 '거의' 차이가 없다 또는 같은 전압을 갖는다라고 말할 수 있는 것이다. (0.9999999... = 1로 표현하는 것과 같다.)

하지만 내가 적은 멘트에는 '보통'이라는 표현이 섞여있다.

그렇지 않은 경우도 있다는 것이다.

이 경우는 다음 포스팅에서 살펴보겠다.

② 두 입력 단자로 전류가 들어가지 않는다.

우선 OP-Amp를 사용하는 상황이라면 특정 신호를 증폭시키는 역할을 기대할 것이다.

이 경우 입력단에서 신호를 잘 받는 능력이 아주 중요하다 !!

그렇다면 신호를 잘 받기 위해선 어떻게 해야할까?

아래 회로를 떠올려 보자.

우선 처음보는 기호에 대해 설명하겠다.

가운데 물결 표시가 있는 회로 기호는 교류 전압원 (AC Voltage Source), 아래쪽 짝대기 3개로 표현된 단자는 그라운드(GND, Ground)라고 하며 0V 전위를 뜻한다.

교류가 무슨 말인지 모르겠다면 이전 포스팅에서 설명한 것을 참조하라.

#7.5 교류(AC)와 직류(DC) - E와 I (MBTI)

오늘 살펴볼 교류와 직류는 살면서 자주 들어봤을 단어일 것이다. 일단 자세한 설명에 앞서 장단점 및 둘의 차이가 요약된 표를 먼저 볼 것이다. 그냥 그렇구나~ 라고 눈대중을 찍은 후 하기 자

enfj-electronics.tistory.com

교류 신호 Vs가 연결된 직렬 저항 Rs를 거쳐 Rin으로 전달된다고 가정해보자.

직렬 회로이므로 같은 전류가 흐를 것이고 고로 Rin이 Rs보다 매우 크다면, 대부분의 신호가 Rin에 할당될 것이다.

위 원리를 이용하여 연산증폭기를 만들 때, 입력단에서 바라본 저항 Rin을 매우 크게 만든다.

그래야만 대부분의 신호가 입력단에 전달될 것이기 때문이다.

이때, 입력단에서 바라본 저항 성분을 입력 임피던스(Input Impedance, Zin)라고 표현한다.

(임피던스라는 개념은 아직 배우지 않았지만 일단은 저항과 비슷하다고 생각해두자.)

요약하자면 연산증폭기는 입력한 신호를 잘 전달받기 위해 입력 임피던스가 매우 크게 만들어 Open된 것과 같이 보이므로, 두 입력단자로 전류가 흐르지 않는다고 생각하면 된다.

#5.5 단락(Short)과 개방(Open) - 끊을까? 이을까?

물이 흐르는 수로를 생각해보자. 서로 다른 물줄기를 수로로 이어버린다면? 물줄기가 하나가 되어 흐른다. 반대로 물이 잘 흐르고 있는 수로를 막아버린다면? 원래 흐르던 방향으로 물이 흐르지

enfj-electronics.tistory.com

추가적으로 출력단도 고려해보자.

증폭기 내부적으로 만든 증폭된 출력 신호가 위 그림에서의 Vs라고 가정해보자.

Vs에서 내부 출력 저항 Rs를 거친다고 생각해보면, 뒷 단의 Rin으로 신호를 잘 전달하는 것이 목적일 것이다.

따라서 입력 저항이 커야하는 것과 반대로 연산증폭기의 출력 저항(또는 출력 임피던스, Output Impedance, Zout)는 작을수록 좋다.

오늘 설명한 내용을 종합하여 OP-Amp의 내부 구조를 정리하자면 아래와 같다.

한 가지 헷갈릴 수 있는 포인트가 있다.

위 그림을 제대로 이해했다면 알 수 있겠지만 전류가 흐르지 않는 것은 두 입력단에 국한될 뿐, 출력단에서는 전류가 흐른다.

KCL이나 KVL 방정식을 세울 때 헷갈리지 않도록 유의하자 !

(필자 주변에 이걸 모르는 사람을 자주 봤다.)

오늘은 신호를 증폭시켜 크게 볼 수 있는 연산증폭기에 대해 알아보았다.

작은 것을 확대하여 크게 볼 수 있는 돋보기와 같은 역할을 가진 회로 소자로 기억해주었으면 한다.

또한 본 내용을 제대로 숙지해야만 다음 포스팅에서 살펴볼 연산증폭기의 다양한 회로들의 이해에 도움이 될 것이다 ↓

#10-1. 연산 증폭기(OP-Amp) 활용법 - 반전/비반전 회로

앞서 살펴본 연산 증폭기의 원리를 토대로 다양한 회로를 구성해볼 것이다. #9. 연산 증폭기 (OP-Amp) - 신호 돋보기오늘은 연산증폭기라고 하는 새로운 소자에 대해 알아볼 것이다.전공자들은 주

enfj-electronics.tistory.com

#10-2. 연산 증폭기(OP-Amp) 활용법 - 비교기와 버퍼

이전 포스팅 #10에선 OP-Amp의 동작원리를 알아보았고 #9. 연산 증폭기 (OP-Amp) - 신호 돋보기오늘은 연산증폭기라고 하는 새로운 소자에 대해 알아볼 것이다.전공자들은 주로 OP-Amp ('오피 앰프'라고

enfj-electronics.tistory.com

몇 번이고 다시 보며 이해하고 내 멘트에 공감해보도록 하자.

잘 모르겠다면 댓글로 남겨달라.

시간 날 때마다 살펴보겠다.

읽어줘서 감사하다 ^~^

'회로이론' 카테고리의 다른 글

| #10-2. 연산 증폭기(OP-Amp) 활용법 - 비교기와 버퍼 (32) | 2024.06.20 |

|---|---|

| #10-1. 연산 증폭기(OP-Amp) 활용법 - 반전/비반전 회로 (36) | 2024.06.19 |

| #9. 델타-와이 (Δ-Y) 변환 및 증명 - 병렬도, 직렬도 아니라고? (38) | 2024.06.11 |

| #8. 교류(AC)와 직류(DC) - E와 I (MBTI) (34) | 2024.06.09 |

| #7. 테브난/노턴 등가회로 - 위정척사 (38) | 2024.06.04 |